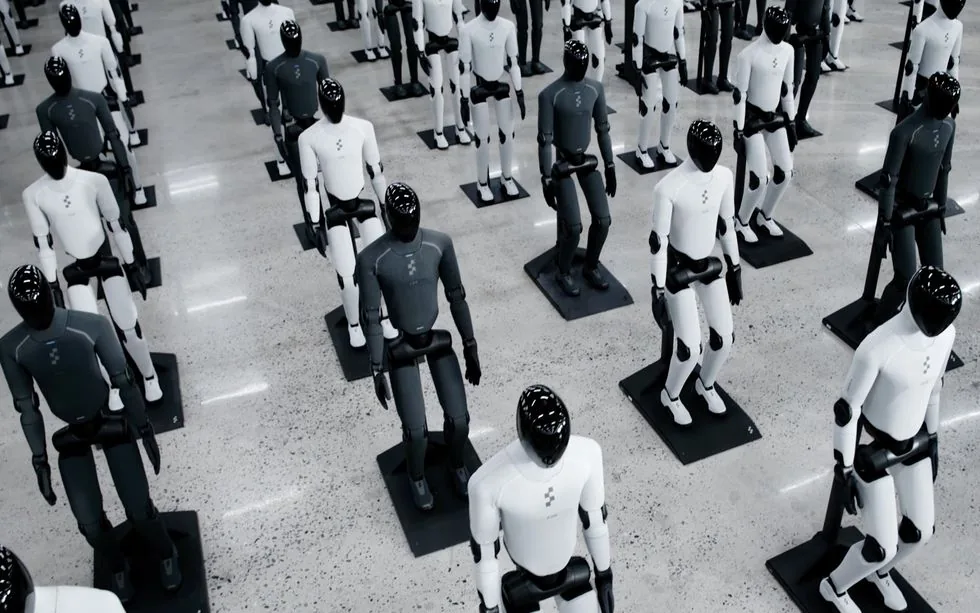

Muchos de los sistemas electrónicos más avanzados del mundo (routers de Internet, estaciones base inalámbricas, escáneres de imagen médica y algunas herramientas de inteligencia artificial) dependen de field-programmable gate arrays, los FPGAs: chips con circuitos de hardware internos que pueden reconfigurarse después de la fabricación.

El 12 de marzo de 2026, una placa IEEE Milestone que reconoce al primer FPGA fue dedicada en el campus de Advanced Micro Devices en San Jose, California, antigua sede de Xilinx y lugar de nacimiento de la tecnología. El FPGA recibió la designación porque introdujo la iteración al diseño de semiconductores: los ingenieros podían rediseñar hardware repetidamente sin fabricar un chip nuevo, lo que reduce drásticamente el riesgo de desarrollo y permite innovación más rápida.

¿Qué problema resolvió el FPGA en los años ochenta?

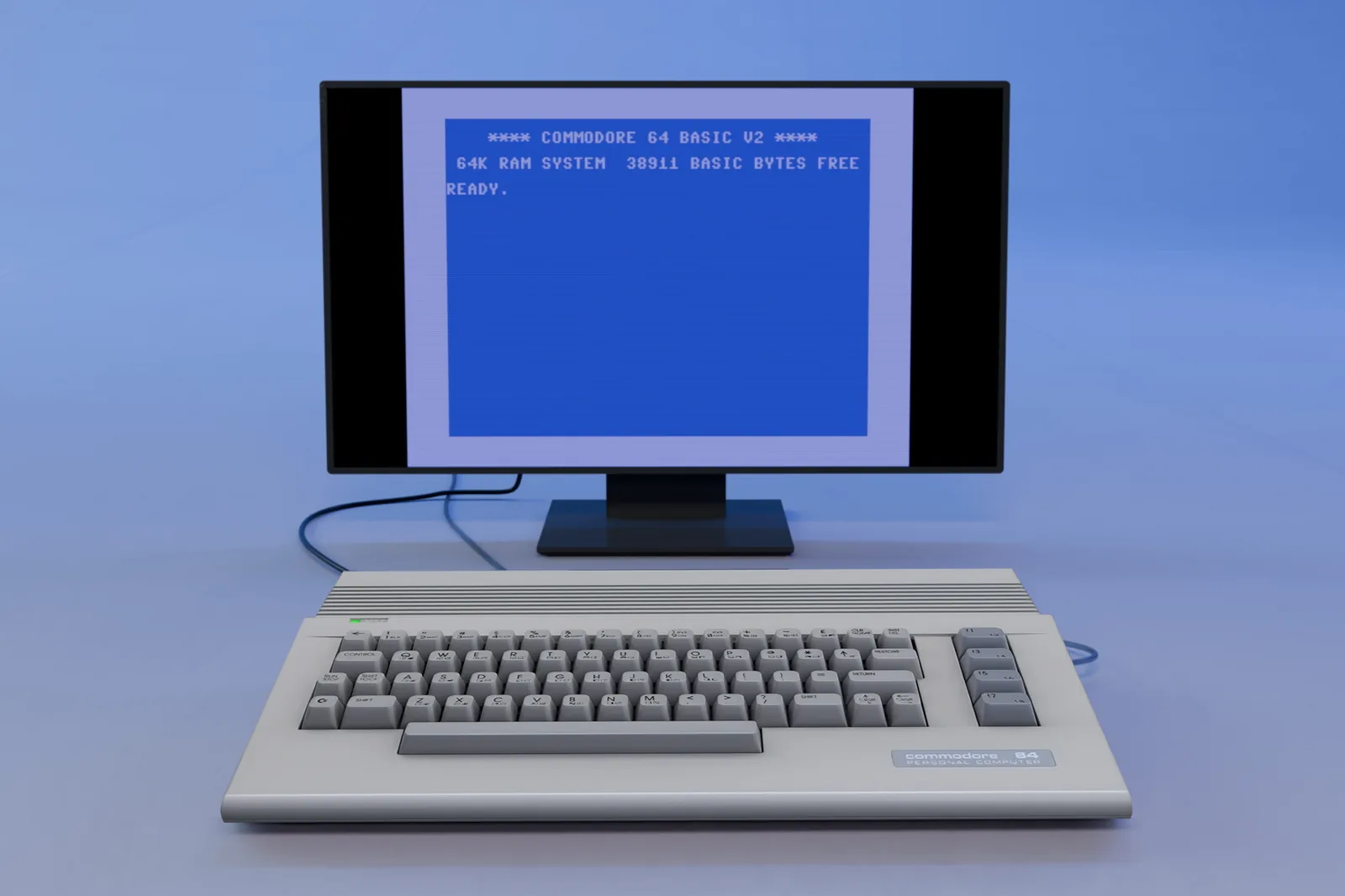

Los FPGA emergieron en los años 80 para resolver una limitación central de la computación. Un microprocesador ejecuta instrucciones de software de forma secuencial: es flexible pero a veces demasiado lento para cargas que requieren muchas operaciones en paralelo. En el otro extremo, los circuitos integrados de aplicación específica (ASIC) están diseñados para hacer una sola tarea. Son extremadamente eficientes pero requieren ciclos de desarrollo largos y costos de ingeniería no recurrentes (NRE) altísimos.

"Los ASIC pueden entregar el mejor rendimiento, pero el ciclo de desarrollo es largo y el costo no recurrente puede ser muy alto", dice Jason Cong, IEEE Fellow y profesor de ciencias de la computación en UCLA. "Los FPGA proveen un punto dulce entre procesadores y silicio custom".

El trabajo fundacional de Cong en automatización de diseño FPGA y síntesis de alto nivel cambió cómo se programan los sistemas reconfigurables. Por ejemplo, desarrolló herramientas de síntesis que traducen C/C++ directamente a diseños de hardware.

¿Quién inventó el primer FPGA?

La arquitectura FPGA se originó a mediados de los 80 en Xilinx, una empresa de Silicon Valley fundada en 1984. La invención se atribuye ampliamente a Ross Freeman, cofundador de Xilinx y CTO de la startup. Freeman imaginó un chip cuyos circuitos pudieran configurarse después de la fabricación en lugar de quedar fijados permanentemente durante la creación.

En la época, los ingenieros de semiconductores trataban a los transistores como un recurso escaso. Los chips custom estaban cuidadosamente optimizados para que casi cada transistor sirviera un propósito específico. Freeman propuso un enfoque distinto: imaginó que la Ley de Moore pronto cambiaría la economía de los chips. A medida que los transistores se volvieran abundantes, la flexibilidad importaría más que la eficiencia perfecta.

Freeman a veces comparó el concepto con una cinta de cassette en blanco: el fabricante provee el medio, mientras que el ingeniero determina su función. La analogía capturó un cambio profundo en quién controla la tecnología, trasladando la flexibilidad del diseño de hardware desde las fábricas hacia los propios diseñadores de sistemas.

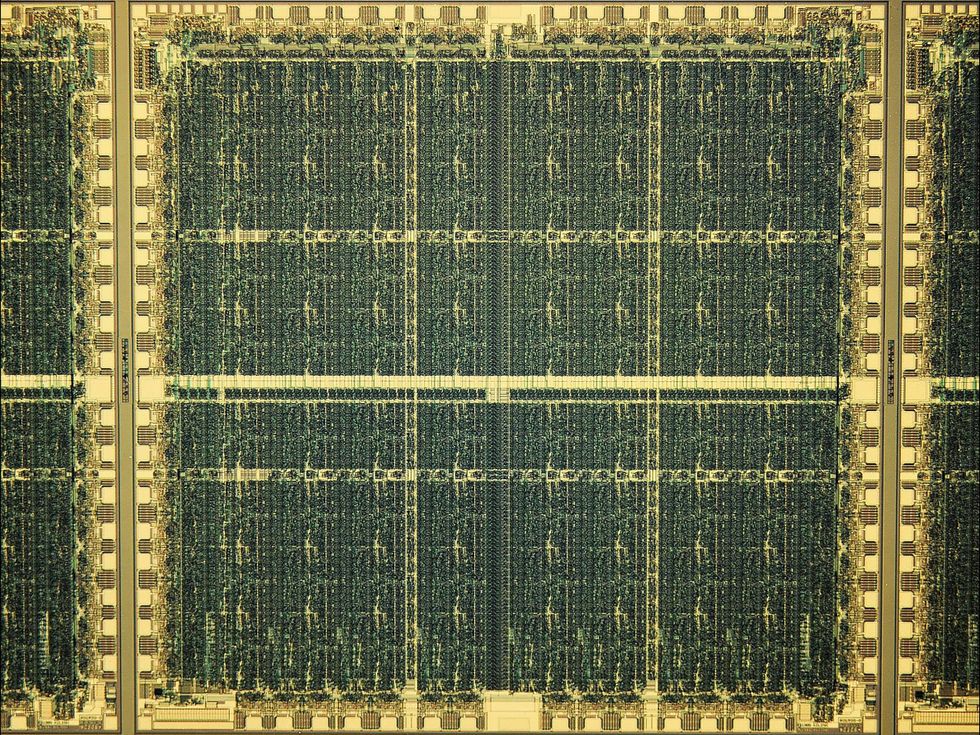

¿Qué tenía el XC2064 por dentro?

En 1985 Xilinx introdujo el primer FPGA en venta comercial: el XC2064. El dispositivo contenía 64 bloques lógicos configurables (pequeños circuitos digitales capaces de realizar operaciones lógicas) organizados en una grilla de 8 por 8. Canales de ruteo programables permitían a los ingenieros definir cómo se movían las señales entre bloques, "cableando" un circuito custom mediante software.

Fabricado con un proceso de 2 micrómetros, el XC2064 implementaba apenas unos pocos miles de compuertas lógicas. Los FPGAs modernos contienen cientos de millones de compuertas, habilitando diseños mucho más complejos. Pero el XC2064 estableció un workflow de diseño que se sigue usando hoy: los ingenieros describen el comportamiento del hardware digitalmente y luego "compilan el diseño", un proceso que traduce automáticamente los planos en instrucciones que el FPGA necesita para configurar sus bloques lógicos y su cableado, según AMD. Después se carga esa configuración al chip.

¿Qué hizo distinto al FPGA frente a los EPROM?

Los dispositivos lógicos programables anteriores, como las EPROM (memorias programables borrables de solo lectura), permitían personalización limitada pero dependían de estructuras de cableado fijas que no escalaban bien al crecer la complejidad de los circuitos, según Cong.

Los FPGA introdujeron interconexiones programables: redes de switches electrónicos controlados por celdas de memoria distribuidas en el chip. Cuando se enciende, el dispositivo carga un archivo de configuración llamado bitstream que determina cómo se comportan sus circuitos internos. "A medida que la tecnología de proceso mejoró y el conteo de transistores creció, el costo de la programabilidad se volvió mucho menos significativo", dice Cong.

¿Cómo pasó de "glue logic" a infraestructura crítica?

"Inicialmente los FPGAs se usaron como lo que los ingenieros llaman glue logic", dice Cong. Glue logic refiere a circuitos simples que conectan procesadores, memoria y periféricos para que el sistema funcione de manera confiable, especialmente cuando las interfaces cambian con frecuencia.

Los primeros adoptantes reconocieron la ventaja de un hardware que podía adaptarse cuando los estándares evolucionaban. En el paper "The History, Status, and Future of FPGAs" publicado en Communications of the ACM, ingenieros de Xilinx y organizaciones como Bell Labs, Fairchild Semiconductor, IBM y Sun Microsystems explican que los primeros usos del FPGA fueron prototipar ASICs y validar sistemas complejos corriendo su software antes de la fabricación. Esto permitía desplegar productos especializados en volúmenes modestos.

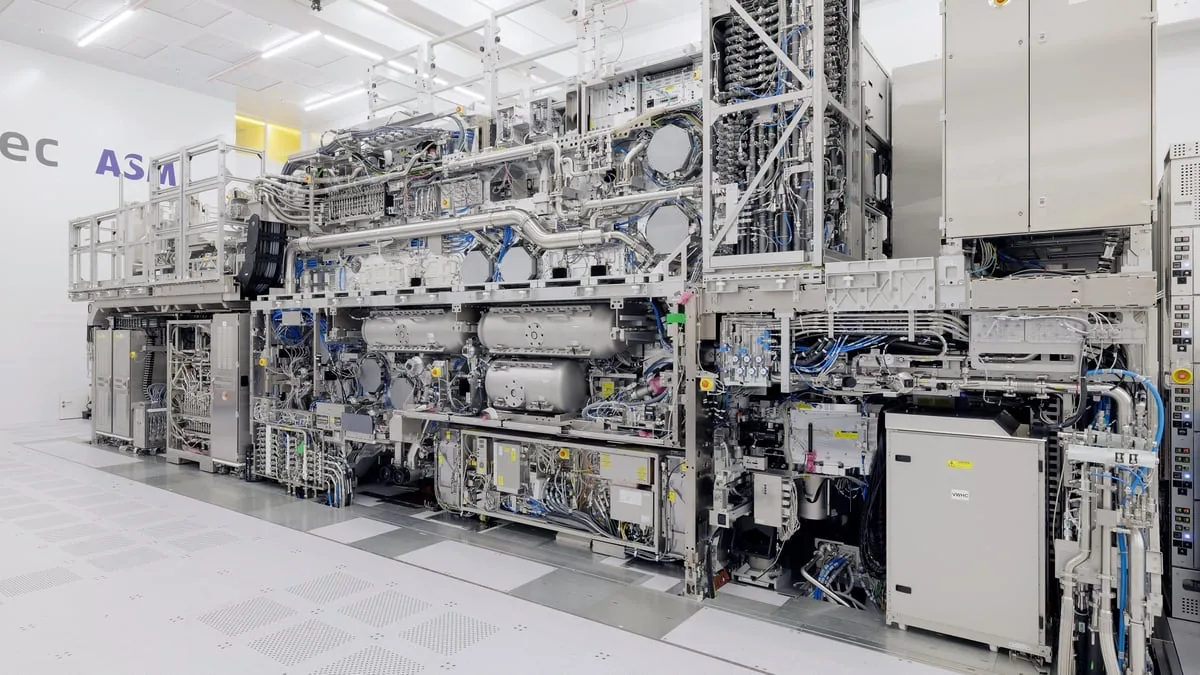

¿Por qué cambió la economía de los chips?

El despegue del FPGA siguió de cerca a los cambios en la economía de los semiconductores. Desarrollar un chip custom requiere una gran inversión upfront antes de empezar la producción. A medida que los costos de fabricación subieron, los productos tenían que enviarse en grandes cantidades para que el desarrollo ASIC fuera económicamente viable. Los FPGAs permitieron a los diseñadores avanzar sin ese compromiso financiero mayor.

El desarrollo ASIC requiere típicamente 18 a 24 meses desde la concepción hasta el silicio, mientras que las implementaciones FPGA pueden completarse en 3 a 6 meses con herramientas modernas, según Cong. El ciclo más corto y la capacidad de reconfigurar el hardware permitieron a startups, universidades y fabricantes experimentar con arquitecturas avanzadas antes accesibles solo para empresas grandes.

¿Y las lookup tables y la computación reconfigurable?

Una técnica popular para implementar funciones matemáticas en hardware es la lookup table (LUT): un pequeño elemento de memoria que almacena los resultados de operaciones lógicas. En lugar de recalcular los resultados cada vez, el chip recupera las respuestas directamente desde la memoria. Cong compara el enfoque con consultar las tablas de multiplicar en vez de recomputar la aritmética.

Investigaciones lideradas por Cong y otros desarrollaron metodologías eficientes que llevaron a la computación reconfigurable a la frontera de la inferencia LLM. Un paper titulado "LUT-LLM: Efficient Large Language Model Inference with Memory-based Computations on FPGAs", aceptado para el 34th IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM) del próximo mes, demuestra cómo correr inferencia de modelos de lenguaje usando LUTs.

La placa IEEE Milestone marca formalmente el cierre de un ciclo: lo que en 1985 era un compromiso entre flexibilidad y rendimiento, hoy es uno de los fundamentos sobre los que corren routers de Internet, estaciones base 5G, aceleradores de IA en el edge y prototipos de los próximos chips de IA.